Filter Design HDL Coder 는 MATLAB 으로 설계된 고정소수점 필터를 FPGA 또는 ASIC에서 구현하기 위해 합성 가능하고 이식 가능한 VHDL® 및Verilog® 코드를 생성합니다. 생성된 코드의 시뮬레이션, 테스트 및 검증을 위한 VHDL 및 Verilog 테스트 벤치를 자동으로 생성합니다.

시작하기:

Filter Design HDL Coder 는 DSP System Toolbox 와 통합되어 단일화된 설계 및 구현 환경을 제공합니다. MATLAB 커맨드라인이나 DSP System Toolbox에서 Filter Designer 앱 또는 Filter Builder 앱을 사용하여 필터를 설계하고 VHDL 및 Verilog 코드를 생성할 수 있습니다.

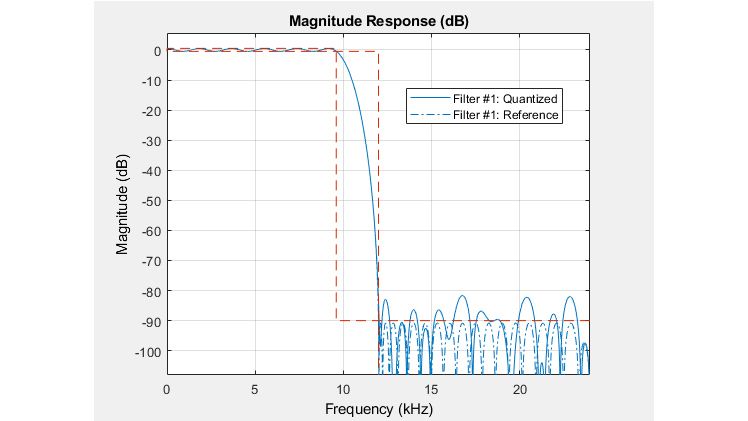

Filter Design HDL Coder에 대한 설계 입력은 양자화된 필터이며, 다음과 같은 두가지 방법으로 생성할 수 있습니다.

- DSP System Toolbox를 사용하여 필터 설계 및 양자화

- Signal Processing Toolbox 로 필터 설계 및 DSP System Toolbox로 양자화

Filter Design HDL Coder는 다음을 비롯한 여러 중요한 필터 구조를 지원합니다.

이산시간 유한 임펄스 응답(FIR) - 대칭, 비대칭, 전치 구조 포함

2차섹션형(SOS) 무한 임펄스 응답(IIR) - 디렉트 폼 I, II 및 전치 구조 포함

멀티레이트 필터 - CIC(cascaded integrator-comb) 보간기 및 간축기, 디렉트 폼 FIR 및 전치 FIR 다상 보간기 및 간축기, FIR 유지 및 선형 보간기, FIR 다상 샘플 레이트 변환기 구조 포함

분수 지연 필터 - Farrow 구조 포함

Filter Design HDL Coder는 다단 멀티레이트 및 이산시간 필터로부터 HDL 코드를 생성할 수 있습니다. 이러한 각각의 싱글레이트 및 멀티레이트 필터 구조는 고정소수점 및 부동소수점(배정밀도) 실현을 지원합니다. FIR 구조는 이에 더해 부호 없는 고정소수점 계수도 지원합니다.

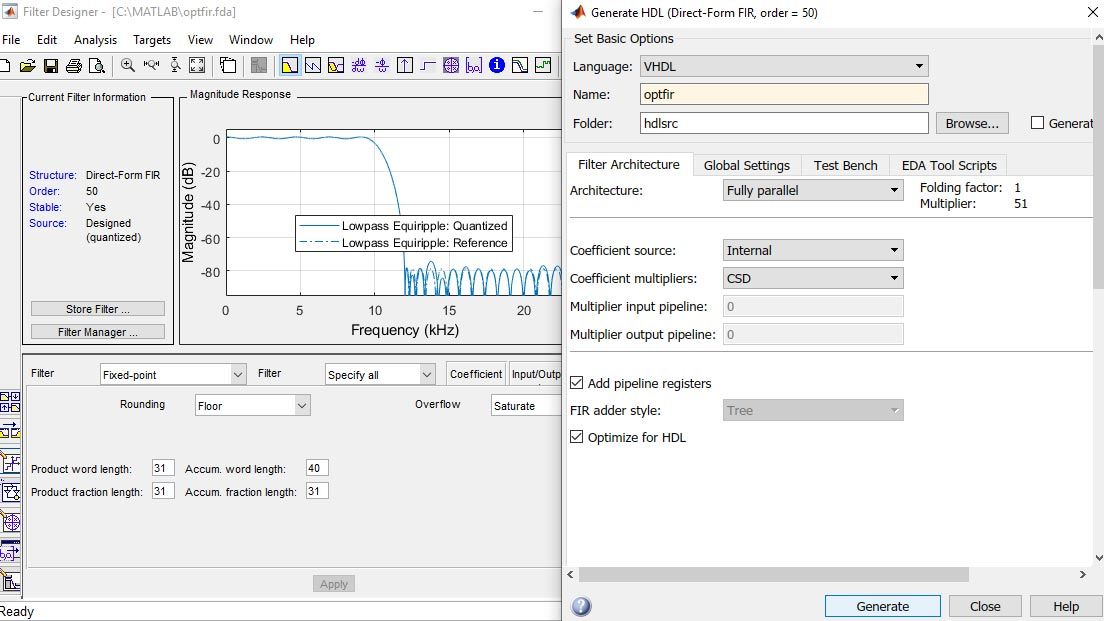

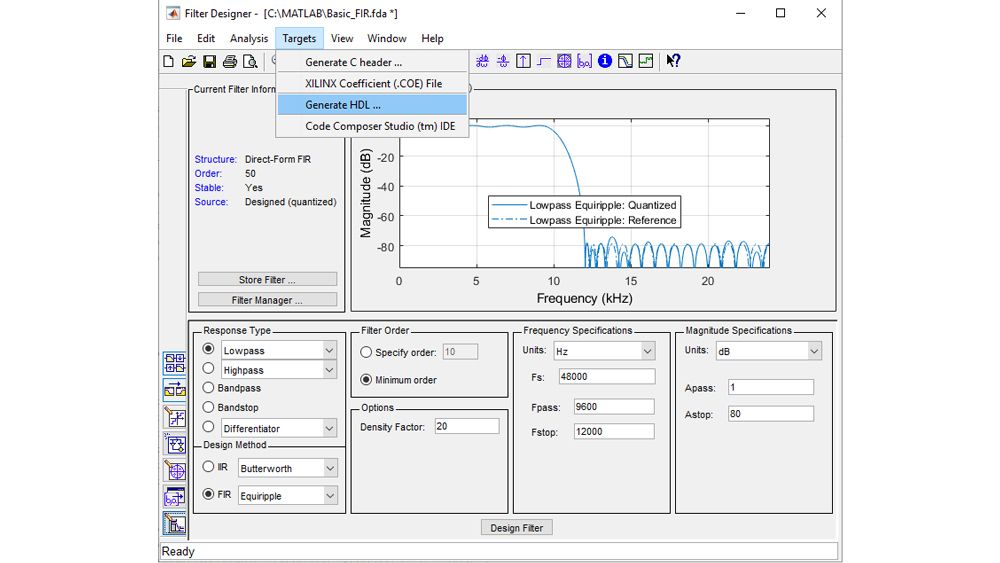

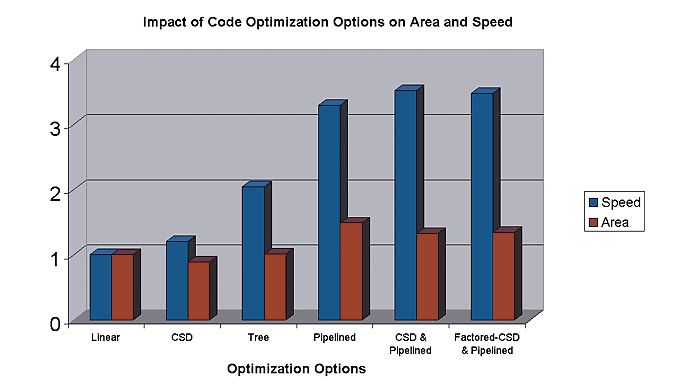

Filter Designer 앱 또는 Filter Builder 앱에서 고정소수점 필터를 위한 VHDL 또는 Verilog 코드를 생성할 수 있습니다. 이들 앱 중 하나로 HDL 코드를 생성할 때 구현 아키텍처를 지정하고, 포트 데이터 유형을 선택하고, 파이프라인 레지스터를 삽입하는 등의 동작을 수행하도록 HDL 생성 옵션을 설정할 수 있습니다. 그 밖에도 필터 HDL 설계의 테스트 벤치를 생성 및 구성하는 옵션을 사용할 수 있습니다.

Filter Design HDL Coder는 옵션 설정 또는 속성 이름과 속성 값 쌍을 바탕으로 양자화된 필터의 필터 및 테스트 벤치 HDL 코드를 생성합니다. 이러한 설정을 통해 다음을 수행할 수 있습니다.

- 언어 요소에 이름 지정

- 포트 파라미터 지정

- 고급 HDL 코딩 기능 사용

모든 속성에는 디폴트 설정이 있습니다. Filter Design and Analysis 앱 또는 Filter Builder 앱으로 설정을 조정하여 HDL 출력값을 사용자 지정할 수 있습니다. 앱을 사용하여 다음과 관련된 속성을 설정할 수 있습니다.

- HDL 언어 사양

- 파일 이름 및 위치 사양

- 리셋 사양

- HDL 코드 최적화

- 테스트 벤치 사용자 지정

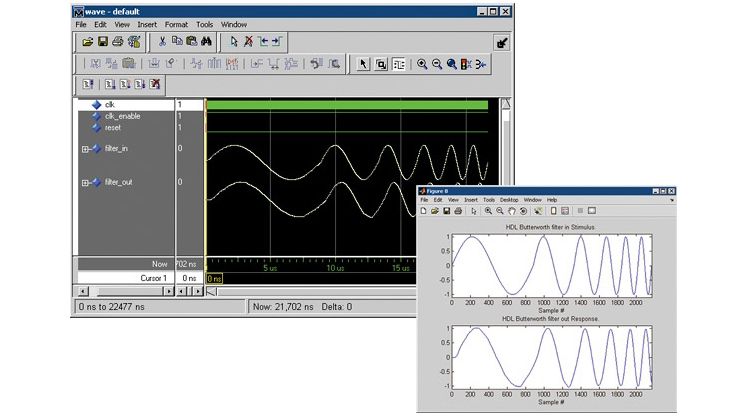

VHDL 또는 Verilog 테스트 벤치를 생성하여 생성된 HDL 코드를 시뮬레이션 및 테스트할 수 있습니다. 이에 더해 HDL Verifier 를 사용하여 Simulink 코시뮬레이션 블록을 생성하여 Simulink에서 실행되는 동작 필터 모델 및 테스트를 Cadence® Incisive® 및 Xcelium™ 시뮬레이터 또는 Mentor® ModelSim® 및 Questa® 시뮬레이터에서 실행되는 자동생성된 HDL에 연결할 수 있습니다. 코시뮬레이션은 생성된 HDL 코드의 결과와 Simulink에서 실행되는 동작 필터 모델의 결과를 직접 비교하여 필터 설계를 간편하게 검증할 수 있도록 지원합니다. 이러한 통합을 바탕으로 MATLAB 및 Simulink의 고급 분석 및 시각화 기능을 적용하여 필터 설계의 HDL 구현을 테스트, 디버그 및 검증할 수 있습니다.